- 您现在的位置:买卖IC网 > Sheet目录1220 > IP-ED8B10B (Altera)IP 8B10B ENCODER/DECODER

�� �

�

�

�3–6�

�Chapter� 3:� Specifications�

�Functional� Description�

�When� the� register� inputs/outputs� parameter� is� turned� off,� the� encoder� takes� one� clock�

�cycle� to� encode� a� character.� The� encoded� value—corresponding� to� the� values� of�

�datain� and� kin� sampled� by� the� encoder� on� rising� edge� n� —is� output� shortly� after�

�rising� edge� n� ,� and� is� available� to� be� sampled� on� the� rising� edge� of� clock� cycle� n+1� .� (See�

�Figure� 3–6� ).�

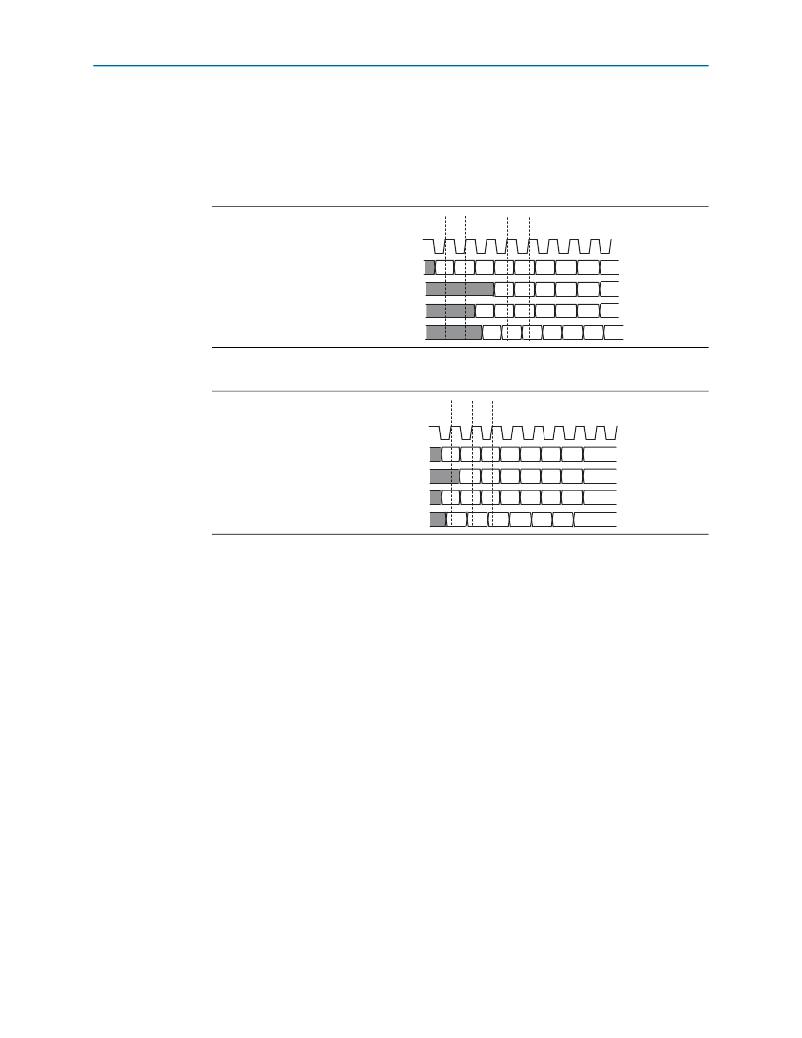

�Figure� 3–5.� Encoder� Timing� Diagram—Three� Cycle� Latency�

�clk�

�n�

�n+1� n+2� n+3�

�datain,� kin,� en,� idle_ins�

�datao� u� t,� rdo� u� t,� kerr,� v� alid�

�rdforce,� rdin�

�rdcascade�

�a�

�b�

�c�

�a�

�a�

�d�

�a�

�b�

�b�

�e�

�b�

�c�

�c�

�f�

�c�

�d�

�d�

�g�

�d�

�e�

�e�

�e�

�f�

�f�

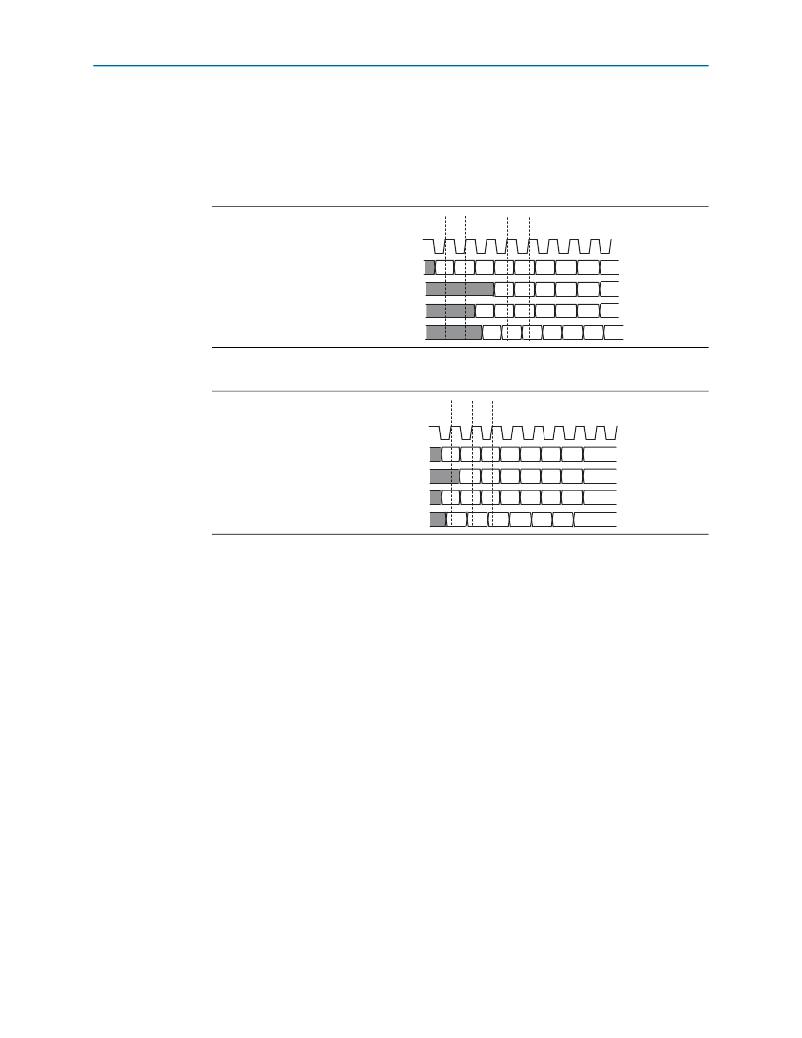

�Figure� 3–6.� Encoder� Timing� Diagram—One� Cycle� Latency�

�clk�

�n�

�n+1�

�datain,� kin,� en,� idle_ins�

�datao� u� t,� rdo� u� t,� kerr,� v� alid�

�rdforce,� rdin�

�rdcascade�

�a�

�a�

�a�

�b�

�a�

�b�

�b�

�c�

�b�

�c�

�c�

�d�

�c�

�d�

�d�

�e�

�d�

�e�

�e�

�f�

�e�

�f�

�f�

�g�

�f�

�g�

�g�

�Fibre� Channel� and� IEEE� 802.3z� 1000BaseX�

�In� Fibre� Channel� and� IEEE� 802.3z� 1000BaseX� applications� the� encoder� does� not�

�automatically� select� the� correct� 8-bit� data� for� Fibre� Channel� EOF� or� 1000BaseX� Idle�

�ordered� sets.� The� running� disparity� based� selection� of� the� correct� 8-bit� data� must� be�

�made� before� passing� the� data� to� the� encoder.�

�Decoder�

�Data� and� identified� 10-bit� special� K� codes� are� converted� from� 10� bits� to� 8� bits;� see�

�Table� 3–1� on� page� 3–3� for� a� list� of� the� valid� K� codes,� and� Figure� 3–1� on� page� 3–1� for� an�

�illustration� of� the� conversion� process.�

�When� special� 10-bit� K� codes� are� received,� the� special� K� codes� are� translated� to� 8-bit�

�values,� and� the� kout� signal� is� asserted.� The� decoder� also� checks� for� invalid� 10-bit�

�codes.�

�When� the� decoder� receives� an� invalid� code,� it� asserts� the� kerr� signal� and� decodes� the�

�value� to� an� arbitrary� number.�

�1�

�The� decoder� flags� the� 10B_ERR� characters� as� invalid� codes� and� asserts� the�

�kerr� signal.�

�When� the� idle_del� signal� is� asserted,� it� deletes� all� 10-bit� words� identified� as� the�

�special� IDLE� character� of� K28.5.�

�8B10B� Encoder/Decoder� MegaCore� Function� User� Guide�

�May� 2011� Altera� Corporation�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IP-FFT

IP FFT/IFFT

IP-FIR

IP FIR COMPILER

IP-NCO

IP NCO COMPILER

IP-NIOS

IP NIOS II MEGACORE

IP-PCI/MT64

IP PCI 64BIT MASTER/TARGET

IP-PCIE/8

IP PCI EXPRESS, X8

IP-POSPHY4

IP POS-PHY L4

IP-RIOPHY

IP RAPID I/O

相关代理商/技术参数

IPEH-002021E

制造商:Phytec 功能描述:PCAN-USB

IPF039N03L G

功能描述:MOSFET N-CH 30V 50A 3.9mOhms RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube

IPF039N03LG

制造商:INFINEON 制造商全称:Infineon Technologies AG 功能描述:OptiMOS?3 Power-Transistor Features Fast switching MOSFET for SMPS

IPF04N03LA

功能描述:MOSFET N-CH 25V 50A DPAK RoHS:否 类别:分离式半导体产品 >> FET - 单 系列:OptiMOS™ 标准包装:1,000 系列:MESH OVERLAY™ FET 型:MOSFET N 通道,金属氧化物 FET 特点:逻辑电平门 漏极至源极电压(Vdss):200V 电流 - 连续漏极(Id) @ 25° C:18A 开态Rds(最大)@ Id, Vgs @ 25° C:180 毫欧 @ 9A,10V Id 时的 Vgs(th)(最大):4V @ 250µA 闸电荷(Qg) @ Vgs:72nC @ 10V 输入电容 (Ciss) @ Vds:1560pF @ 25V 功率 - 最大:40W 安装类型:通孔 封装/外壳:TO-220-3 整包 供应商设备封装:TO-220FP 包装:管件

IPF04N03LA G

功能描述:MOSFET N-CH 25V 50A DPAK RoHS:是 类别:分离式半导体产品 >> FET - 单 系列:OptiMOS™ 标准包装:1,000 系列:MESH OVERLAY™ FET 型:MOSFET N 通道,金属氧化物 FET 特点:逻辑电平门 漏极至源极电压(Vdss):200V 电流 - 连续漏极(Id) @ 25° C:18A 开态Rds(最大)@ Id, Vgs @ 25° C:180 毫欧 @ 9A,10V Id 时的 Vgs(th)(最大):4V @ 250µA 闸电荷(Qg) @ Vgs:72nC @ 10V 输入电容 (Ciss) @ Vds:1560pF @ 25V 功率 - 最大:40W 安装类型:通孔 封装/外壳:TO-220-3 整包 供应商设备封装:TO-220FP 包装:管件

IPF04N03LAG

功能描述:MOSFET N-Channel MOSFET 20-200V RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube

IPF04N03LBG

制造商:INFINEON 制造商全称:Infineon Technologies AG 功能描述:OptiMOS㈢2 Power-Transistor

IPF050N03LG

功能描述:MOSFET N-Channel MOSFET 20-200V RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube